高串數模擬前端

高串數模擬前端

相關文章 : 1篇

瀏覽 : 21次

針對具有1 nF傳感電容和5μA平均幅度的隨機電流脈沖的核探測器,設計了一種基于跨阻放大器(TIA)的模擬前端.核心放大器采用單端折疊共源共柵結構提高帶寬和速度,采用增益增強(gain-boosted)技術以滿足高增益的要求.模擬前端基于SMIC 40 nm CMOS工藝設計實現,仿真結果表明,核心放大器在電源電壓1.1 V下,增益帶寬積為2.2 GHz,增益為72.3 dB,模擬前端在閉環增益為500Ω和1 nF傳感電容時,可以實現22 MHz的閉環帶寬,模擬前端的總功耗為3.2 mW.

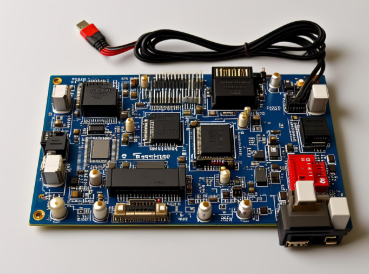

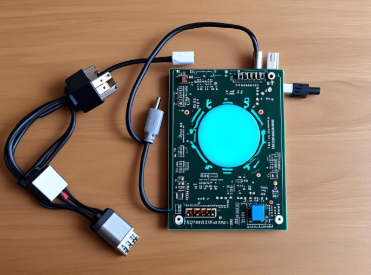

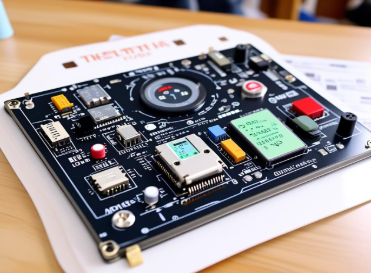

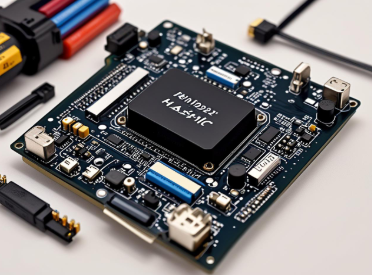

推薦產品

列表欄目

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)