為什么以及如何使用Efinix FPGA進(jìn)行AI/ML成像第2部分:圖像捕獲和處理

160

160

拍明芯城

拍明芯城

作者:Adam Taylor

編者注:FPGA 架構(gòu)的新方法帶來了更細(xì)粒度的控制和更大的靈活性,可以滿足機(jī)器學(xué)習(xí) (ML) 和人工智能 (AI) 的需求。這個(gè)由兩部分組成的系列的第 1 部分介紹了Efinix的一種此類架構(gòu)以及如何使用開發(fā)板開始使用它。在這里,第 2 部分討論將開發(fā)板連接到外部設(shè)備和外設(shè)(例如相機(jī)),以及如何利用 FPGA 消除圖像處理瓶頸。

FPGA 在許多應(yīng)用中發(fā)揮著關(guān)鍵作用,從工業(yè)控制和安全到機(jī)器人、航空航天和汽車。由于可編程邏輯內(nèi)核的靈活性及其廣泛的接口功能,F(xiàn)PGA 的一個(gè)不斷增長的用例是圖像處理,可以在其中部署機(jī)器學(xué)習(xí) (ML)。由于其并行邏輯結(jié)構(gòu),F(xiàn)PGA 非常適合實(shí)現(xiàn)具有多個(gè)高速攝像頭接口的解決方案。此外,F(xiàn)PGA 還支持在邏輯中使用專用處理管道,從而消除與基于 CPU 或 GPU 的解決方案相關(guān)的共享資源瓶頸。

對(duì) Efinix 的Titanium FPGA的第二次觀察將檢查 FPGA 的Ti180 M484開發(fā)板附帶的參考圖像處理應(yīng)用程序。目的是了解設(shè)計(jì)的組成部分,并確定 FPGA 技術(shù)在哪些方面可以消除瓶頸或?yàn)殚_發(fā)人員帶來其他好處。

基于 Ti180 M484 的參考設(shè)計(jì)

從概念上講,參考設(shè)計(jì)(圖 1)從多個(gè)移動(dòng)行業(yè)處理器接口 (MIPI) 攝像頭接收?qǐng)D像,在 LPDDR4x 中執(zhí)行幀緩沖,然后將圖像輸出到高清多媒體接口 (HDMI) 顯示器。 FPGA 夾層卡 (FMC) 和板上的四個(gè)Samtec QSE接口用于提供相機(jī)輸入和 HDMI 輸出。

圖 1:從概念上講,Ti180 M484 參考設(shè)計(jì)從多個(gè) MIPI 相機(jī)接收?qǐng)D像,在 LPDDR4x 中執(zhí)行幀緩沖,然后將圖像輸出到 HDMI 顯示器。 >(圖片來源:Efinix)

FMC至 QSE 擴(kuò)展卡與 HDMI 子卡一起使用以提供輸出視頻路徑,而三個(gè) QSE 連接器用于連接 DFRobot SEN0494 MIPI相機(jī)。如果多個(gè) MIPI 攝像頭不可用,則可以通過環(huán)回單個(gè)攝像頭通道來使用單個(gè)攝像頭來模擬其他攝像頭。

從高層次上看,此應(yīng)用程序可能看起來很簡(jiǎn)單。然而,以高幀率接收多個(gè)高清 (HD) MIPI 流具有挑戰(zhàn)性。這就是 FPGA 技術(shù)的優(yōu)勢(shì)所在,因?yàn)樗试S設(shè)計(jì)人員并行利用多個(gè) MIPI 流。

參考設(shè)計(jì)的架構(gòu)利用 FPGA 的并行和順序處理結(jié)構(gòu)。并行結(jié)構(gòu)用于實(shí)現(xiàn)圖像處理流水線,而 RISC-V 處理器提供用于 FPGA 查找表 (LUT) 的順序處理。

在許多基于 FPGA 的圖像處理系統(tǒng)中,圖像處理流水線可以分為兩個(gè)元素,即輸入流和輸出流。輸入流連接到相機(jī)/傳感器接口,處理功能應(yīng)用于傳感器的輸出。這些功能可以包括拜耳轉(zhuǎn)換、自動(dòng)白平衡和其他增強(qiáng)功能。在輸出流中,圖像已準(zhǔn)備好顯示。這包括更改顏色空間(例如,RGB 到 YUV)和對(duì)所需輸出格式(例如 HDMI)的后處理。

通常,輸入圖像處理鏈以傳感器像素時(shí)鐘速率運(yùn)行。這與以輸出顯示頻率處理的輸出鏈具有不同的時(shí)序。

幀緩沖區(qū)用于將輸入連接到輸出處理管道,通常存儲(chǔ)在外部高性能存儲(chǔ)器中,例如 LPDDR4x。該幀緩沖器在輸入和輸出管道之間解耦,允許以適當(dāng)?shù)臅r(shí)鐘頻率通過直接存儲(chǔ)器訪問來訪問幀緩沖器。

Ti180 參考設(shè)計(jì)使用與上述概念類似的方法。輸入圖像處理管道實(shí)現(xiàn)了一個(gè) MIPI 相機(jī)串行接口 2 (CSI-2) 接收器知識(shí)產(chǎn)權(quán) (IP) 內(nèi)核,它建立在 MIPI 物理層 (MIPI D-PHY) 的輸入/輸出 (I/O) 之上鈦FPGA。 MIPI 是一個(gè)具有挑戰(zhàn)性的接口,因?yàn)槌说退俸透咚偻ㄐ胖猓€使用同一差分對(duì)上的單端和差分信號(hào)。在 FPGA I/O 中集成 MIPI D-PHY 降低了電路卡設(shè)計(jì)的復(fù)雜性,同時(shí)還減少了物料清單 (BOM)。

收到來自攝像頭的圖像流后,參考設(shè)計(jì)將 MIPI CSI-2 RX 的輸出轉(zhuǎn)換為高級(jí)可擴(kuò)展接口 (AXI) 流。 AXI Stream 是一種單向高速接口,可提供從主機(jī)到從機(jī)的數(shù)據(jù)流。提供用于在主設(shè)備和從設(shè)備之間傳輸?shù)奈帐中盘?hào)(tvalid 和 tready)以及邊帶信號(hào)。這些邊帶信號(hào)可用于傳送圖像定時(shí)信息,例如幀開始和行結(jié)束。

AXI Stream 是圖像處理應(yīng)用的理想選擇,使 Efinix 能夠提供一系列圖像處理 IP,然后可以根據(jù)應(yīng)用的需要輕松集成到處理鏈中。

MIPI CSI-2圖像數(shù)據(jù)和時(shí)序信號(hào)接收后,轉(zhuǎn)換為AXI Stream,輸入直接內(nèi)存訪問(DMA)模塊,將圖像幀寫入LPDDR4x,作為幀緩存。

該 DMA 模塊在藍(lán)寶石片上系統(tǒng) (SoC) 內(nèi)的 FPGA 中的 RISC-V 內(nèi)核的控制下運(yùn)行。除了為 DMA 寫入通道提供必要信息以將圖像數(shù)據(jù)正確寫入 LPDDR4x 之外,該 SoC 還提供停止和啟動(dòng) DMA 寫入等控制。這包括有關(guān)存儲(chǔ)位置的信息以及以字節(jié)為單位定義的圖像的寬度和高度。

參考設(shè)計(jì)中的輸出通道在 RISC-V SoC 的控制下從 LPDDR4x 幀緩沖區(qū)讀取圖像信息。數(shù)據(jù)作為 AXI 流從 DMA IP 輸出,然后從傳感器提供的 RAW 格式轉(zhuǎn)換為 RGB 格式(圖 2),并準(zhǔn)備通過板載 Analog Devices 的 ADV7511 HDMI 發(fā)射器 輸出。

圖 2:參考設(shè)計(jì)輸出的示例圖像。 (圖片來源:亞當(dāng)·泰勒)

DMA 的使用還使 Sapphire SoC RISC-V 能夠訪問存儲(chǔ)在幀緩沖區(qū)中的圖像,以及抽象統(tǒng)計(jì)數(shù)據(jù)和圖像信息。 Sapphire SoC 還能夠?qū)B加層寫入 LPDDR4x,以便它們可以與輸出視頻流合并。

現(xiàn)代 CMOS 圖像傳感器 (CIS) 具有多種操作模式,可配置為提供片上處理,以及多種不同的輸出格式和時(shí)鐘方案。此配置通常通過 I2C 接口提供。在 Efinix 參考設(shè)計(jì)中,這種與 MIPI 相機(jī)的 I2C 通信由 Sapphire SoC RISC-V 處理器提供。

將 RISC-V 處理器集成到 Titanium FPGA 中可減少最終解決方案的整體尺寸,因?yàn)樗鼰o需實(shí)施會(huì)增加設(shè)計(jì)風(fēng)險(xiǎn)的復(fù)雜 FPGA 狀態(tài)機(jī),也無需實(shí)施會(huì)增加 BOM 的外部處理器。

包含處理器還支持使用額外的 IP 與 MicroSD 卡進(jìn)行通信。這使得現(xiàn)實(shí)世界的應(yīng)用程序可能需要存儲(chǔ)圖像以供以后分析。

總體而言,Ti180 參考設(shè)計(jì)的架構(gòu)經(jīng)過優(yōu)化,可實(shí)現(xiàn)緊湊、低成本但高性能的解決方案,使開發(fā)人員能夠通過系統(tǒng)集成降低 BOM 成本。

參考設(shè)計(jì)的主要優(yōu)勢(shì)之一是它們可用于在定制硬件上啟動(dòng)應(yīng)用程序開發(fā),使開發(fā)人員能夠采用設(shè)計(jì)的關(guān)鍵元素并根據(jù)需要進(jìn)行定制。這包括使用 Efinix 的 TinyML 流程來實(shí)現(xiàn)在 FPGA 上運(yùn)行的基于視覺的 TinyML 應(yīng)用程序的能力。這可以利用 FPGA 邏輯的并行特性和將自定義指令輕松添加到 RISC-V 處理器的能力,從而允許在 FPGA 邏輯中創(chuàng)建加速器。

執(zhí)行

正如第 1 部分中所討論的,Efinix 架構(gòu)的獨(dú)特之處在于它使用可交換邏輯和路由 (XLR) 單元來提供路由和邏輯功能。像參考設(shè)計(jì)這樣的視頻系統(tǒng)是一個(gè)混合系統(tǒng),邏輯和布線都很繁重:需要大量的邏輯來實(shí)現(xiàn)圖像處理功能,并且需要大量的布線來以所需的頻率連接 IP 單元。

該參考設(shè)計(jì)在設(shè)備中使用了大約 42% 的 XLR 單元,為添加提供了充足的空間,包括自定義應(yīng)用程序,例如 edge ML。

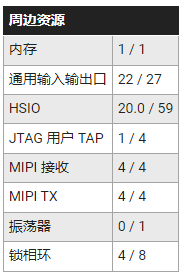

塊 RAM 和數(shù)字信號(hào)處理 (DSP) 塊的使用也非常高效,僅使用 640 個(gè) DSP 塊中的 4 個(gè)和 40% 的內(nèi)存塊(圖 3)。

圖 3:Efinix 架構(gòu)上的資源分配顯示僅使用了 42% 的 XLR 單元,為其他進(jìn)程留下了充足的空間。 (圖片來源:亞當(dāng)·泰勒)

在設(shè)備 IO 上,LPDDR4x 的 DDR 接口用于為 Sapphire SoC 和圖像幀緩沖區(qū)提供應(yīng)用程序內(nèi)存。所有設(shè)備專用的 MIPI 資源都與 50% 的鎖相環(huán)一起使用(圖 4)。

圖 4:所用接口和 I/O 資源的快照。 (圖片來源:亞當(dāng)·泰勒)

通用 I/O (GPIO) 用于提供 I2C 通信以及連接到 Sapphire SoC 的多個(gè)接口,包括 NOR FLASH、USB UART 和 SD 卡。 HSIO 用于向 ADC7511 HDMI 發(fā)送器提供高速視頻輸出。

使用 FPGA 進(jìn)行設(shè)計(jì)的關(guān)鍵要素之一不僅是在 FPGA 內(nèi)實(shí)施和適配設(shè)計(jì),而且能夠?qū)⑦壿嬙O(shè)計(jì)置于 FPGA 內(nèi)并在布線時(shí)實(shí)現(xiàn)所需的時(shí)序性能。

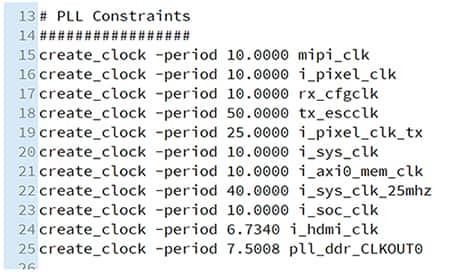

單時(shí)鐘域 FPGA 設(shè)計(jì)的時(shí)代早已一去不復(fù)返了。 Ti180 參考設(shè)計(jì)中有幾種不同的時(shí)鐘,它們都以高頻運(yùn)行。最終時(shí)序表顯示了系統(tǒng)內(nèi)時(shí)鐘達(dá)到的最大頻率。這就是要求的時(shí)序性能也可以在約束中看到(圖 5),HDMI 輸出時(shí)鐘的最大時(shí)鐘頻率為 148.5 兆赫茲 (MHz)。

圖 5:參考設(shè)計(jì)的時(shí)鐘約束。 (圖片來源:亞當(dāng)·泰勒)

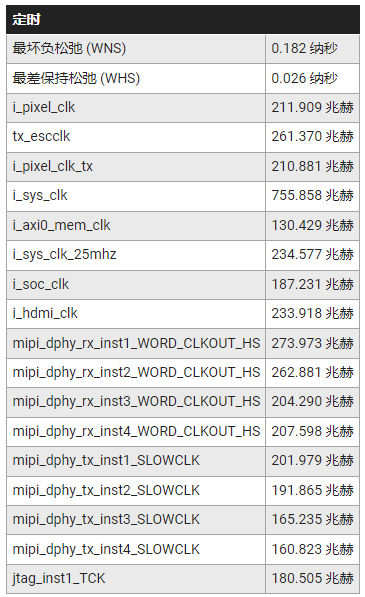

針對(duì)約束的時(shí)序?qū)崿F(xiàn)顯示了 Titanium FPGA XLR 結(jié)構(gòu)的潛力,因?yàn)樗鼫p少了可能的路由延遲,從而提高了設(shè)計(jì)性能(圖 6)。

圖 6:針對(duì)約束的時(shí)序?qū)崿F(xiàn)顯示了 Titanium FPGA XLR 結(jié)構(gòu)在減少可能的路由延遲方面的潛力,從而提高了設(shè)計(jì)性能。 (圖片來源:亞當(dāng)·泰勒)

結(jié)論

Ti180 M484 參考設(shè)計(jì)清楚地展示了 Efinix FPGA 的功能,尤其是 Ti180。該設(shè)計(jì)利用多個(gè)獨(dú)特的 I/O 結(jié)構(gòu)來實(shí)現(xiàn)支持多個(gè)傳入 MIPI 流的復(fù)雜圖像處理路徑。該圖像處理系統(tǒng)在軟核藍(lán)寶石 SoC 的控制下運(yùn)行,該系統(tǒng)實(shí)現(xiàn)了應(yīng)用程序的必要順序處理元素。

責(zé)任編輯:David

【免責(zé)聲明】

1、本文內(nèi)容、數(shù)據(jù)、圖表等來源于網(wǎng)絡(luò)引用或其他公開資料,版權(quán)歸屬原作者、原發(fā)表出處。若版權(quán)所有方對(duì)本文的引用持有異議,請(qǐng)聯(lián)系拍明芯城(marketing@iczoom.com),本方將及時(shí)處理。

2、本文的引用僅供讀者交流學(xué)習(xí)使用,不涉及商業(yè)目的。

3、本文內(nèi)容僅代表作者觀點(diǎn),拍明芯城不對(duì)內(nèi)容的準(zhǔn)確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨(dú)立判斷做出的,請(qǐng)讀者明確相關(guān)結(jié)果。

4、如需轉(zhuǎn)載本方擁有版權(quán)的文章,請(qǐng)聯(lián)系拍明芯城(marketing@iczoom.com)注明“轉(zhuǎn)載原因”。未經(jīng)允許私自轉(zhuǎn)載拍明芯城將保留追究其法律責(zé)任的權(quán)利。

拍明芯城擁有對(duì)此聲明的最終解釋權(quán)。

產(chǎn)品分類

產(chǎn)品分類

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)