基于ADRV9002敏捷射頻收發器實現在航空航天和國防的自適應SDR通信系統設計方案

27

27

拍明芯城

拍明芯城

斯蒂芬·埃萬丘克

航空航天和國防 (ADEF) 系統設計人員面臨著對更低功耗、更緊湊的通信系統的不懈需求,這些系統能夠對動態信號環境做出敏捷響應。超越傳統的無線電架構,軟件定義無線電 (SDR) 技術可以幫助滿足 ADEF 無線電快速變化的要求,但 SDR 的實施給滿足功能要求以及減小尺寸、重量和功耗的需求帶來了多重挑戰(交換)。

本文介紹了Analog Devices的一種更有效的 SDR 解決方案,該解決方案可以簡化低功耗、緊湊且靈活的通信系統的設計,而不會影響性能。

新的挑戰帶來更苛刻的要求

設計人員在越來越多的工業和關鍵任務應用中面臨著對更有效通信的需求,包括安全無線電通信、自適應雷達、電子戰和增強型 GPS 導航。這些新挑戰推動了對增強寬帶操作、更高動態范圍、更大頻率捷變性和可重構性的需求。然而,隨著通信系統轉向更小的電池供電平臺(包括無人機(UAS)和便攜式設備),這些更苛刻的功能要求可能與較低 SWaP 的需求相沖突。

基于傳統離散超外差無線電架構的設計解決方案提供高性能、寬動態范圍和最小的雜散噪聲。對于設計人員來說,這種方法的核心是將所需信號與中頻 (IF) 隔離的挑戰通常會導致設計復雜、SWaP 高且可重構性極低甚至沒有(圖 1)。

圖 1:傳統的超外差無線電架構可以滿足性能目標,但其復雜性使其無法滿足新興的最小 SWaP 目標。 (圖片來源:Analog Devices)

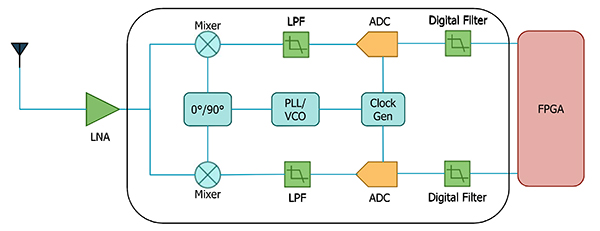

相比之下,直接轉換(零中頻)架構降低了濾波要求以及對極高帶寬模數轉換器 (ADC) 的需求,從而實現了可以在單芯片上實現的更簡單的設計(圖 2) )。

圖 2:零中頻無線電架構可以滿足更高性能和更低 SWaP 的需求,但信號隔離具有挑戰性。 (圖片來源:Analog Devices)

盡管直接轉換架構具有明顯的優勢,但其自身的實施挑戰限制了其廣泛采用。在此架構中,信號被轉換為本地振蕩器 (LO) 頻率的射頻 (RF) 載波,但直流 (DC) 偏移誤差和 LO 泄漏可能導致誤差通過信號鏈傳播。此外,即使在同一芯片內,信號路徑的差異也會導致同相 (I) 和正交 (Q) 信號的增益或相位失配,從而導致正交誤差,進而影響信號隔離。

SDR 技術具有克服傳統無線電架構限制的潛力,但很少有解決方案能夠滿足與 ADEF 應用相關的更廣泛要求。使用 Analog Devices 的ADRV9002 RF 收發器,開發人員可以輕松滿足這些應用中對更高性能和功能的需求,并降低 SWaP 的要求。

集成功能可提供優化的性能并減少 SWaP

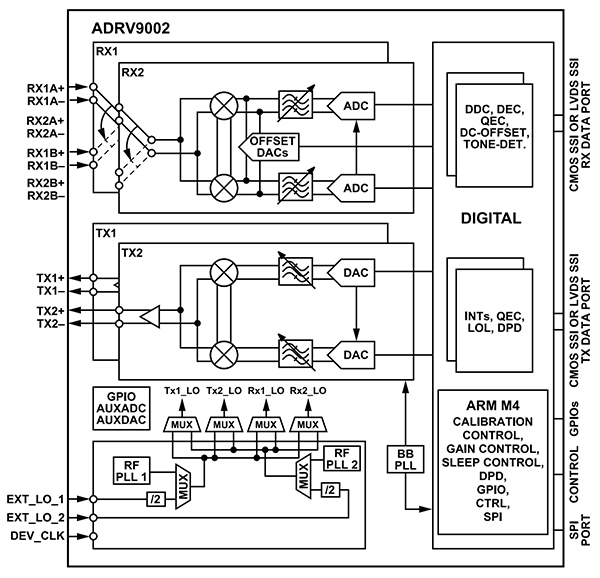

ADRV9002 支持 30 兆赫 (MHz) 至 6,000 MHz 的頻率范圍,是一款高度集成的收發器,包含支持各種應用要求所需的所有射頻、混合信號和數字功能。該器件能夠進行時分雙工 (TDD) 和頻分雙工 (FDD) 操作,具有獨立的雙通道直接轉換接收器和發送器子系統,其中包括可編程數字濾波器、直流偏移校正和正交誤差校正 (QEC)。

在其片上合成器子系統中,ADRV9002 具有兩個不同的鎖相環 (PLL) 路徑:一個用于高頻 RF 路徑,另一個用于數字時鐘和轉換器采樣時鐘。最后,該器件的數字信號處理模塊包括一個Arm? M4 嵌入式處理器,用于處理自校準和控制功能(圖 3)。

圖 3:ADRV9002 RF 收發器集成了雙接收 (RX) 和發送 (TX) 子系統。 (圖片來源:Analog Devices)

ADRV9002 能夠在零中頻模式或低中頻模式下運行,適用于相位噪聲敏感型應用,其發射器和接收器子系統可提供完整的信號鏈。每個發射器子系統都提供一對數模轉換器 (DAC)、濾波器和混頻器,用于重新組合 I 和 Q 信號并將其調制到載波頻率上進行傳輸。

每個接收器子系統都集成了一個用于增益控制的電阻輸入網絡,該網絡為電流模式無源混頻器供電。反過來,跨阻放大器將混頻器的電流輸出轉換為由具有高動態范圍的 ADC 數字化的電壓電平。在 TDD 操作或僅使用一個接收器系統的 FDD 應用中的可用發送器時隙期間,未使用的接收器輸入可用于監控發送器通道的 LO 泄漏和 QEC,或者未使用的接收器輸入可用于監控功率放大器 (PA) 輸出信號電平。

后一種功能在 ADRV9002 的集成數字預失真 (DPD) 功能中發揮作用,該功能使用其監控的 PA 信號電平來應用線性化輸出所需的適當預失真。此功能使 ADRV9002 能夠使 PA 接近飽和,從而優化其效率。

調整功率和性能

ADRV9002 器件在 196 球芯片級封裝 (CSP) 球柵陣列 (BGA) 中提供完全集成的解決方案,并最大限度地減少 SDR ADEF 通信系統的尺寸和重量。為了幫助開發人員進一步優化功耗,ADRV9002集成了多種專門設計的功能,幫助開發人員在性能和功耗之間找到合適的平衡點。

在模塊級別,開發人員可以在各個信號路徑模塊上部署功率縮放,以降低性能來換取更低的功耗。此外,可以禁用 TDD 接收 (RX) 和發送 (TX) 幀中的模塊,以犧牲 RX/TX 或 TX/RX 周轉時間來降低功耗。為了進一步幫助開發人員優化功耗與性能的能力,每個 ADRV9002 接收器子系統都包含兩對 ADC。一對包含高性能 Σ-Δ ADC,而第二對可以在功耗至關重要時進行替代。

對于以周期性不活動為特征的應用,可以采用 ADRV9002 的 RX 監控模式。在此模式下,ADRV9002 按編程的占空比在最小功耗睡眠狀態和檢測狀態之間交替。在檢測狀態下,設備激活接收器并嘗試在開發人員編程的帶寬和 RX LO 頻率上獲取信號。如果設備測量到的信號功率電平高于編程閾值,設備將退出監控模式,并且 ADRV9002 的模塊將通電以處理所需的信號。

快速原型設計和開發

為了幫助工程師快速進行評估、原型設計和開發,ADI 公司為基于 ADRV9002 的系統提供了廣泛的硬件和軟件支持。

對于硬件支持,Analog Devices 提供了一對基于 ADRV9002 的卡:

ADRV9002NP/W1/PCBZ適用于在 30 MHz 至 3 GHz 范圍內運行的低頻段應用

ADRV9002NP/W2/PCBZ適用于 3 至 6 GHz 范圍內的高頻段應用

這些卡配備 FMC 連接器,支持板載 ADRV9002 的電源調節和硬件接口,以及時鐘和多芯片同步 (MCS) 分配。這些卡通過 FMC 連接器連接到 FPGA 主板,例如用于電源和應用控制的AMD ZCU102評估板。

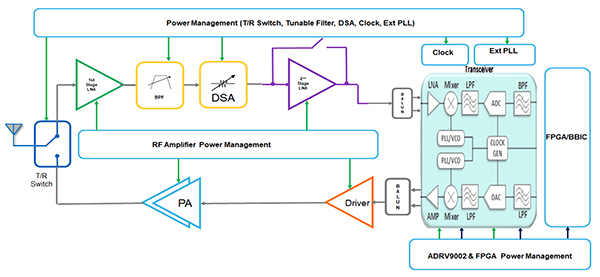

Analog Devices 在其支持包中為其 ADRV9002NP 無線電卡提供了完整的原理圖和物料清單 (BOM)。原理圖和 BOM 為大多數應用的定制硬件開發提供了有效的起點。某些應用需要額外的射頻前端來滿足特定的信號調理要求。對于這些應用程序,開發人員只需要一些額外的組件即可完成其設計(圖 4)。

圖 4:高度集成的 ADRV9002 收發器使開發人員能夠快速實施專門設計。 (圖片來源:Analog Devices)

在此示例中,開發人員可以使用 Analog Devices 的以下電源管理組件快速實現合適的 RF 前端:

ADRF5160射頻開關

HMC8411低噪聲放大器 (LNA)

ADMV8526數字可調諧帶通濾波器

HMC1119射頻數字步進衰減器 (DSA)

HMC8413驅動放大器

HMC8205B功率放大器

Analog Devices 通過文檔和可下載軟件包提供全面的軟件開發支持。使用上述開發硬件的開發人員可以基于ADI公司的產品線軟件或開源軟件包進行原型設計和開發。

本文將以下討論僅限于產品線軟件。有關開源開發方法的更多信息,請參閱 Analog Devices 的 ADRV9001/2 原型平臺用戶指南。 Analog Devices 規定,公司支持文檔中的術語“ADRV9001”是指涵蓋 ADRV9002 和 ADRV9001 系列其他成員的系列代號。因此,下面的文本或圖中對 ADRV9001 的引用適用于本文重點討論的 ADRV9002 器件。

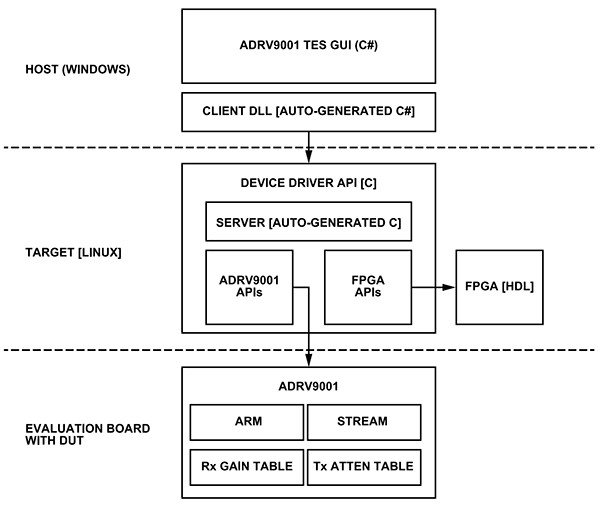

該公司基于 Windows 的收發器評估軟件(TES) 工具通過 Analog Devices 的產品線軟件開發套件 (SDK) 分發提供,為快速配置和評估收發器性能提供了一個易于使用的起點。

在使用 Analog Devices 基于 ADRV9002 的卡和 AMD ZCU102 評估板進行評估和原型設計期間,TES 工具提供了一個圖形用戶界面 (GUI),用于配置硬件和觀察捕獲的數據(圖 5)。

圖 5:SDK 包中的 TES 工具可讓開發人員快速開始在支持的評估平臺上評估 ADRV9002 收發器。 (圖片來源:Analog Devices)

反過來,TES 工具會自動生成可編譯到 Linux 環境、MATLAB 環境或 Python 的 C# 代碼。該SDK提供了一套完整的軟件庫和應用程序編程接口(API),包括為AMD ZCU102平臺開發的ADRV9001 API包。

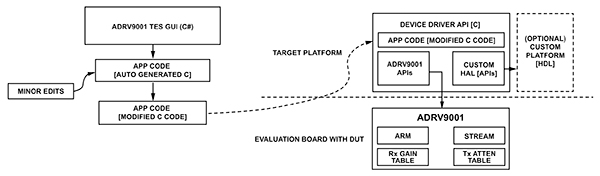

SDK 流程還直接支持從評估板的評估和原型設計遷移到開發人員的自定義目標環境(圖 6)。

圖 6:SDK 架構允許開發人員輕松地將評估結果擴展到自己的目標平臺。 (圖片來源:Analog Devices)

在此遷移流程中,開發人員讓 TES 像以前一樣自動生成代碼。但是,開發人員不是直接使用它,而是將生成的代碼的編輯版本部署到目標平臺。實際上,所需的編輯主要限于刪除引用由 TES 工具識別但目標系統中不需要的硬件組件的函數調用。 SDK 架構包括 ADRV9001 庫和開發人員硬件之間的硬件抽象層 (HAL) 接口,因此開發人員只需提供為其特定硬件實現 HAL 接口代碼的自定義代碼。因此,開發人員可以快速從使用 Analog Devices 卡和 AMD 板的評估轉向針對其自定義目標環境的開發。

結論

ADEF 應用在日益復雜的信號環境中面臨著越來越大的挑戰。除了滿足更廣泛頻率范圍內更高性能的需求外,開發人員還需要降低 SWaP 以支持這些應用程序遷移到電池供電系統。使用 Analog Devices 的高度集成收發器,開發人員可以實施 SDR 解決方案,以更有效地滿足這些要求。

責任編輯:David

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)