如何將 FPGA SoC 用于安全和連接的硬實(shí)時(shí)系統(tǒng)

47

47

拍明芯城

拍明芯城

現(xiàn)場(chǎng)可編程門陣列 (FPGA)、支持 Linux 的 RISC-V 微控制器單元 (MCU) 子系統(tǒng)、高級(jí)存儲(chǔ)器架構(gòu)和高性能通信接口是設(shè)計(jì)人員的重要工具。對(duì)于安全連接系統(tǒng)、安全關(guān)鍵系統(tǒng)以及人工智能 (AI) 和機(jī)器學(xué)習(xí) (ML) 等各種硬實(shí)時(shí)確定性系統(tǒng)的設(shè)計(jì)人員來(lái)說(shuō)尤其如此。

然而,將這些不同的元件集成到一個(gè)安全、互聯(lián)和確定性的系統(tǒng)中可能是一項(xiàng)具有挑戰(zhàn)性和耗時(shí)的活動(dòng),為各種系統(tǒng)元件布置高速互連也是如此。設(shè)計(jì)人員需要包括存儲(chǔ)器管理單元、存儲(chǔ)器保護(hù)單元、安全啟動(dòng)功能和千兆級(jí)收發(fā)器,以實(shí)現(xiàn)高速連接。該設(shè)計(jì)將需要有源和靜態(tài)電源管理以及對(duì)浪涌電流的控制。某些設(shè)計(jì)需要在0°C至+100°C結(jié)溫(TJ),而工業(yè)環(huán)境中的系統(tǒng)將需要在 T 下運(yùn)行J 從 -40°C 到 +100°C。

為了應(yīng)對(duì)這些和其他挑戰(zhàn),設(shè)計(jì)人員可以轉(zhuǎn)向 FPGA 片上系統(tǒng) (SoC) 器件,這些器件結(jié)合了低功耗、熱效率和國(guó)防級(jí)安全性,適用于智能、互聯(lián)和確定性系統(tǒng)。

本文回顧了此類FPGA SoC的架構(gòu),以及它如何支持連接和確定性系統(tǒng)的高效設(shè)計(jì)。然后簡(jiǎn)要介紹EEMBC CoreMark-Pro處理功耗與功耗基準(zhǔn)測(cè)試,以及代表性FPGA SoC的基準(zhǔn)性能視圖。它著眼于如何將安全性融入這些FPGA SoC中,并詳細(xì)介紹了示例性 FPGA 固態(tài)硬盤 從 微芯片技術(shù),以及 開(kāi)發(fā)平臺(tái) 以加快設(shè)計(jì)過(guò)程。最后簡(jiǎn)要列出了來(lái)自 MikroElektronika 可用于實(shí)現(xiàn)一系列通信接口,以及全球?qū)Ш叫l(wèi)星系統(tǒng)(GNSS)定位功能。

采用 FPGA 架構(gòu)構(gòu)建的 SoC

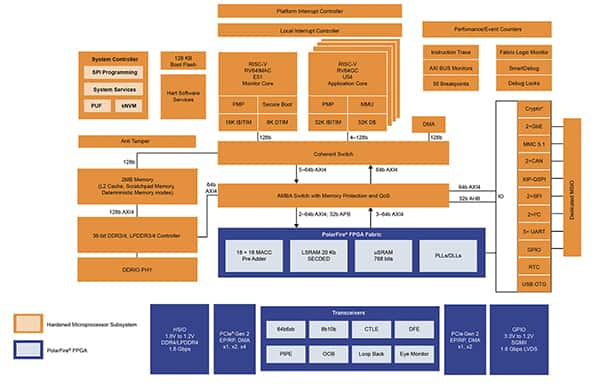

該SoC的“芯片”是一個(gè)FPGA結(jié)構(gòu),其中包含系統(tǒng)元素,從FPGA到使用硬化FPGA邏輯構(gòu)建的RISC-V MCU子系統(tǒng)。MCU 子系統(tǒng)包括一個(gè)四核 RISC-V MCU 集群、一個(gè) RISC-V 監(jiān)控內(nèi)核、一個(gè)系統(tǒng)控制器和一個(gè)確定性 2 級(jí) (L2) 內(nèi)存子系統(tǒng)。這些 SoC 中的 FPGA 包括高達(dá) 460 K 的邏輯元件、高達(dá) 12.7 Gbps 的收發(fā)器以及其他輸入/輸出 (I/O) 模塊,包括通用 I/O (GPIO) 和高速外圍組件互連 (PCIe) 2。整體架構(gòu)專為可靠性而設(shè)計(jì)。它包括所有存儲(chǔ)器上的單錯(cuò)誤校正和雙錯(cuò)誤檢測(cè) (SECDED)、差分功率分析 (DPA)、物理內(nèi)存保護(hù)和 128 kbs 閃存啟動(dòng)存儲(chǔ)器(圖 1)。

圖 1:該 FPGA SoC 中的所有元件(包括 RISC-V 子系統(tǒng))都在 FPGA 架構(gòu)上實(shí)現(xiàn)。(圖片來(lái)源:微芯科技)

Microchip提供其Mi-V(發(fā)音為“我的五”)第三方工具和設(shè)計(jì)資源的生態(tài)系統(tǒng),以支持RISC-V系統(tǒng)的實(shí)施。它旨在加速 RISC-V 指令集架構(gòu) (ISA) 用于強(qiáng)化 RISC-V 內(nèi)核和 RISC-V 軟內(nèi)核。Mi-V 生態(tài)系統(tǒng)的元素包括訪問(wèn):

知識(shí)產(chǎn)權(quán) (IP) 許可

硬件

操作系統(tǒng)和中間件

調(diào)試器、編譯器和設(shè)計(jì)服務(wù)

FPGA SoC 中的強(qiáng)化型 RISC-V MCU 包括多種調(diào)試功能,如無(wú)源運(yùn)行時(shí)可配置高級(jí)可擴(kuò)展接口 (AXI) 和指令跟蹤。AXI 使設(shè)計(jì)人員能夠監(jiān)控寫(xiě)入或讀取各種存儲(chǔ)器的數(shù)據(jù),并了解何時(shí)寫(xiě)入或讀取數(shù)據(jù)。

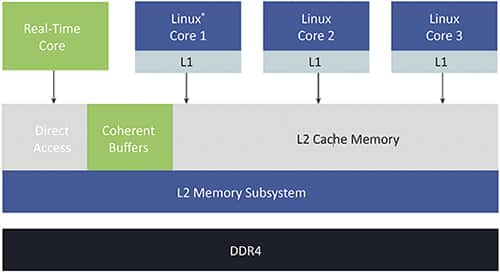

RISC-V MCU 子系統(tǒng)使用五級(jí)單問(wèn)題有序流水線。它不容易受到Spectre或Meltdown漏洞的攻擊,這些漏洞可能會(huì)影響無(wú)序架構(gòu)。所有五個(gè)MCU都與存儲(chǔ)器子系統(tǒng)一致,支持確定性非對(duì)稱多處理(AMP)模式實(shí)時(shí)系統(tǒng)和Linux的混合。RISC-V子系統(tǒng)的功能包括(圖2):

運(yùn)行 Linux 和硬實(shí)時(shí)操作

將 L1 和 L2 配置為確定性存儲(chǔ)器

DDR4 內(nèi)存子系統(tǒng)

禁用/啟用分支預(yù)測(cè)器

按順序管道操作

圖 2:RISC-V 子系統(tǒng)包括多個(gè)處理器和內(nèi)存元件。(圖片來(lái)源:微芯科技)

以更少的能源實(shí)現(xiàn)更多的處理

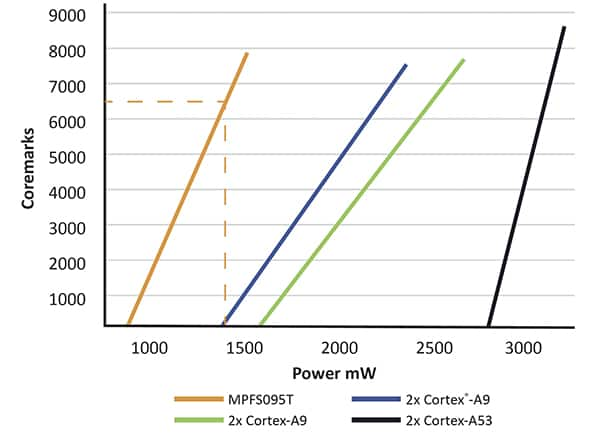

除了系統(tǒng)操作優(yōu)勢(shì)(包括支持硬實(shí)時(shí)處理)外,這些 FPGA SoC 還具有高能效。EEMBC CoreMark-PRO基準(zhǔn)測(cè)試是比較嵌入式系統(tǒng)中MCU效率和性能的行業(yè)標(biāo)準(zhǔn)。它專門設(shè)計(jì)用于基準(zhǔn)測(cè)試硬件性能并取代Dhrystone基準(zhǔn)測(cè)試。

CoreMark-PRO 工作負(fù)載包括基于四個(gè)浮點(diǎn)工作負(fù)載和五個(gè)常見(jiàn)整數(shù)工作負(fù)載的各種性能特征、指令級(jí)并行性和內(nèi)存利用率。浮點(diǎn)工作負(fù)載包括派生自 LINPACK 的線性代數(shù)例程、快速傅里葉變換、用于模式評(píng)估的神經(jīng)網(wǎng)絡(luò)算法以及 Livermore 循環(huán)基準(zhǔn)測(cè)試的改進(jìn)版本。JPEG 壓縮、XML 解析器、ZIP 壓縮和 256 位安全哈希算法 (SHA-256) 構(gòu)成了整數(shù)工作負(fù)載的基礎(chǔ)。

這些 SoC FPGA 的 MPFSO95T 模型,如 MPFS095TL-FCSG536E,可在 1.3 瓦時(shí)提供多達(dá) 6,500 個(gè) Co備注(圖 3)。

圖 3:MPFS095T FPGA SoC(橙色線)以 1.3 瓦的功率提供 6500 個(gè)協(xié)同作用。(圖片來(lái)源:微芯科技)

安全注意事項(xiàng)

這些 FPGA SoC 的安全關(guān)鍵型和硬實(shí)時(shí)應(yīng)用除了需要高能效和強(qiáng)大的處理能力外,還需要強(qiáng)大的安全性。這些 FPGA SoC 的基本安全功能包括抗差分功耗分析 (DPA) 比特流編程、真隨機(jī)數(shù)發(fā)生器 (TRNG) 和物理不可克隆功能 (PUF)。它們還包括標(biāo)準(zhǔn)和用戶定義的安全啟動(dòng)、物理內(nèi)存保護(hù),提供與計(jì)算機(jī)特權(quán)狀態(tài)相關(guān)的內(nèi)存訪問(wèn)限制,包括計(jì)算機(jī)、管理引擎或用戶模式, 以及對(duì)崩潰和幽靈攻擊的免疫力。

安全性始于安全的供應(yīng)鏈管理,包括在晶圓測(cè)試和封裝期間使用硬件安全模塊(HSM)。在每個(gè) FPGA SoC 中嵌入使用 768 字節(jié)數(shù)字簽名的 x.509 FPGA 證書(shū),增加了供應(yīng)鏈保證。

這些 FPGA SoC 中包含許多片上篡改檢測(cè)器,以確保安全可靠的運(yùn)行。如果檢測(cè)到篡改,則會(huì)發(fā)出篡改標(biāo)志,使系統(tǒng)能夠根據(jù)需要做出響應(yīng)。一些可用的篡改檢測(cè)器包括:

電壓監(jiān)視器

時(shí)鐘毛刺和時(shí)鐘頻率檢測(cè)器

JTAG有源探測(cè)器

網(wǎng)狀主動(dòng)檢測(cè)器

通過(guò) 256 位高級(jí)加密標(biāo)準(zhǔn) (AES-256) 對(duì)稱分組密碼相關(guān)功率攻擊 (CPA) 對(duì)策、確保數(shù)據(jù)完整性的集成加密摘要功能、用于密鑰存儲(chǔ)的集成 PUF 以及用于 FPGA 結(jié)構(gòu)和所有片上存儲(chǔ)器的歸零功能,進(jìn)一步確保了安全性。

FPGA SoC 示例

Microchip Technology 將這些功能和技術(shù)結(jié)合到其具有多種速度等級(jí)、溫度額定值和各種封裝尺寸的 PolarFire FPGA SoC 中,以支持設(shè)計(jì)人員對(duì)具有 25 K 至 460 K 邏輯元件的各種解決方案的需求。提供四種溫度等級(jí)(均額定溫度為 TJ)、0°C 至 +100°C 擴(kuò)展商用范圍、-40°C 至 +100°C 工業(yè)范圍、-40°C 至 +125°C 汽車范圍和 -55°C 至 +125°C 軍用范圍。

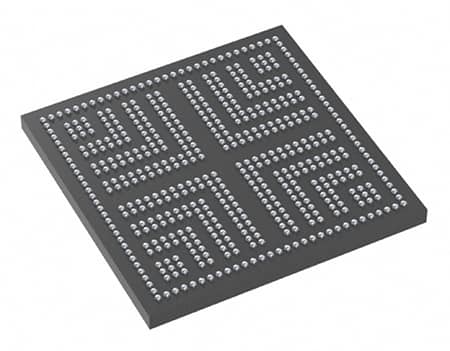

設(shè)計(jì)人員可以選擇標(biāo)準(zhǔn)速度等級(jí)器件,也可以選擇速度快 15% 的 -1 級(jí)器件。這些 FPGA SoC 可在 1.0 V 電壓下運(yùn)行以實(shí)現(xiàn)最低功耗運(yùn)行,或以 1.05 V 電壓運(yùn)行以實(shí)現(xiàn)更高性能。它們提供多種封裝尺寸,包括 11 x 11 毫米 (mm)、16 x 16 mm 和 19 x 19 mm。

對(duì)于需要擴(kuò)展商用溫度操作、標(biāo)準(zhǔn)速度操作和 19 x 19 mm 封裝中的 254 K 邏輯元件的應(yīng)用,設(shè)計(jì)人員可以使用 MPFS250T-FCVG484EES.對(duì)于需要 23 K 邏輯元件的更簡(jiǎn)單解決方案,設(shè)計(jì)人員可以轉(zhuǎn)向 MPFS025T-FCVG484E,還具有擴(kuò)展的商業(yè)溫度操作和標(biāo)準(zhǔn)速度等級(jí),采用 19 x 19 mm 封裝。這 MPFS250T-1FCSG536T2 具有 254 K 邏輯元件,專為高性能汽車系統(tǒng)而設(shè)計(jì),工作溫度范圍為 -40 至 125°C,速度等級(jí)為 -1,時(shí)鐘速度提高了 15%,采用緊湊的 16 x 16 mm 封裝,間距為 0.5 mm 的 536 個(gè)球(圖 4)。

圖 4:汽車溫度 MPFS250T-1FCSG536T2 采用 16 x 16 mm 封裝,球數(shù)為 536,間距為 0.5 mm。(圖片來(lái)源:微芯科技)

FPGA SoC 開(kāi)發(fā)平臺(tái)

為了加快使用PolarFire FPGA SoC的系統(tǒng)設(shè)計(jì),Microchip提供了 強(qiáng)積金-冰柱-套件-ES PolarFire SoC Icicle套件,支持探索具有低功耗實(shí)時(shí)執(zhí)行功能的五核支持Linux的RISC-V微處理器子系統(tǒng)。該套件包括評(píng)估設(shè)計(jì)所需的免費(fèi)Libero Silver許可證。它支持單一語(yǔ)言的編程和調(diào)試功能。

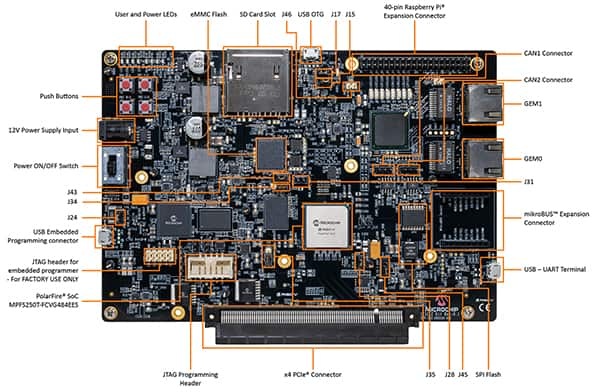

這些 FPGA SoC 受 矢量布洛克斯 加速器軟件開(kāi)發(fā)套件 (SDK),支持低功耗、小尺寸 AI/ML 應(yīng)用。重點(diǎn)是簡(jiǎn)化設(shè)計(jì)過(guò)程,使設(shè)計(jì)人員不需要具有先前的FPGA設(shè)計(jì)經(jīng)驗(yàn)。VectorBlox加速器SDK使開(kāi)發(fā)人員能夠使用C / C++對(duì)高能效神經(jīng)網(wǎng)絡(luò)進(jìn)行編程。Icicle 套件具有眾多功能,可提供全面的開(kāi)發(fā)環(huán)境,包括用于監(jiān)控各種電源域的多軌電源傳感器系統(tǒng)、PCIe 根端口和板載存儲(chǔ)器(包括 LPDDR4、QSPI 和 eMMC 閃存)以運(yùn)行 Linux 和 Raspberry Pi,以及用于大量有線和無(wú)線連接選項(xiàng)的 mikroBUS 擴(kuò)展端口,以及 GNSS 定位功能等功能擴(kuò)展(圖 5)。

圖 5:這個(gè)全面的 FPGA SoC 開(kāi)發(fā)環(huán)境包括用于 Raspberry Pi(右上)和 mikroBUS(右下)擴(kuò)展板的連接器。(圖片來(lái)源:微芯科技)

擴(kuò)展板

mikroBUS 擴(kuò)展板的一些示例包括:

米克羅-986,用于使用串行外設(shè)接口 (SPI) 添加 CAN 總線連接。

米克羅-1582,用于 MCU 和 RS-232 總線之間的接口。

米克羅-989,用于連接 RS422/485 通信總線。

米克羅-3144,支持 LTE Cat M1 和 NB1 技術(shù),可實(shí)現(xiàn)與 3GPP 物聯(lián)網(wǎng)設(shè)備的可靠和簡(jiǎn)單的連接。

米克羅-2670,通過(guò)同時(shí)接收 GPS 和伽利略星座以及北斗或 GLONASS 實(shí)現(xiàn) GNSS 功能,從而在城市峽谷信號(hào)較弱或干擾的情況下實(shí)現(xiàn)高定位精度。

結(jié)論

設(shè)計(jì)人員在開(kāi)發(fā)互聯(lián)、安全關(guān)鍵和硬實(shí)時(shí)確定性系統(tǒng)時(shí)可以求助于 FPGA SoC。FPGA SoC 提供廣泛的系統(tǒng)元件,包括 FPGA 結(jié)構(gòu)、具有高性能存儲(chǔ)器的 RISC-V MCU 子系統(tǒng)、高速通信接口和眾多安全功能。為了幫助設(shè)計(jì)人員入門,我們提供了包含所有必要元素的開(kāi)發(fā)板和環(huán)境,包括可用于實(shí)現(xiàn)各種通信和定位功能的擴(kuò)展板。

責(zé)任編輯:David

【免責(zé)聲明】

1、本文內(nèi)容、數(shù)據(jù)、圖表等來(lái)源于網(wǎng)絡(luò)引用或其他公開(kāi)資料,版權(quán)歸屬原作者、原發(fā)表出處。若版權(quán)所有方對(duì)本文的引用持有異議,請(qǐng)聯(lián)系拍明芯城(marketing@iczoom.com),本方將及時(shí)處理。

2、本文的引用僅供讀者交流學(xué)習(xí)使用,不涉及商業(yè)目的。

3、本文內(nèi)容僅代表作者觀點(diǎn),拍明芯城不對(duì)內(nèi)容的準(zhǔn)確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨(dú)立判斷做出的,請(qǐng)讀者明確相關(guān)結(jié)果。

4、如需轉(zhuǎn)載本方擁有版權(quán)的文章,請(qǐng)聯(lián)系拍明芯城(marketing@iczoom.com)注明“轉(zhuǎn)載原因”。未經(jīng)允許私自轉(zhuǎn)載拍明芯城將保留追究其法律責(zé)任的權(quán)利。

拍明芯城擁有對(duì)此聲明的最終解釋權(quán)。

產(chǎn)品分類

產(chǎn)品分類

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)