全志A10開發板原理圖+PCB源文件

17

17

拍明

拍明

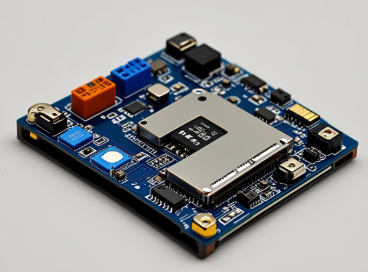

原標題:全志A10開發板原理圖+PCB源文件

全志A10開發板設計方案與原理圖說明

一、概述

全志A10開發板采用全志科技(Allwinner Technology)推出的A10處理器,集成ARM Cortex-A8核、圖形加速器以及多種外設接口。該處理器性能較為均衡、成本經濟,適用于嵌入式多媒體、智能終端與物聯網應用。本文檔旨在介紹一款基于全志A10的開發板,從原理圖與PCB設計入手,詳細說明所選用的元器件型號、元器件作用、選型理由及其功能,包括核心處理器、存儲、時鐘、電源管理、外設接口等各部分內容,并提供具體的參考設計思路和電路要點,以便讀者在進行二次開發或定制化設計時,能夠快速理解各模塊的設計思路以及關鍵器件的選擇依據。

二、核心處理器與存儲部分

全志A10(型號:SUN8i-A10)處理器是該開發板的核心,其內部集成ARM Cortex-A8核(主頻最高可達1.2GHz),并配備NEON協處理器以及Mali-400MP2圖形加速器,可滿足高清視頻解碼與渲染需求。選擇A10的主要原因在于其內置豐富的接口(包括HDMI、LVDS、CSI、USB、以太網等),且具有較高的性價比,適合教育、物聯網、智能家居等多種場景。為了實現系統啟動與數據存儲,通常配置一顆容量為512MB至1GB的DDR2 SDRAM芯片。本文以Micron(美光)MT47H64M16HR-25E DDR2 SDRAM(容量512MB、數據速率400Mbps)為例,之所以選用該型號,是基于其在工作電壓1.8V時的穩定性能、一致性良好以及低成本優勢。此外,該芯片封裝為BGA TSOP,尺寸緊湊,符合多數中小型開發板的布局需求。SDRAM的作用是為Linux內核與各種應用程序提供運行時數據緩存與臨時存儲空間,其槽點在于時序參數較為嚴格,因此在PCB布局時需保證走線長度匹配以及差分布線規范,以確保信號完整性。

為實現系統固件與其他數據存儲,還需配置SPI Nor Flash或eMMC。常見的做法是選用一顆容量為8MB至16MB的SPI NOR Flash用于U-Boot與Bootloader存儲,同時選取一顆容量為4GB或8GB的eMMC用于操作系統與用戶應用程序存儲。在本文參考設計中,選用Winbond(華邦)W25Q64JV(容量8Mb、規格:3.3V、SPI接口)作為NOR Flash,理由是該芯片尺寸適中、價格低廉、可通過SPI總線快速仿真編程以及社區支持豐富;同時選用Samsung(三星)KLMAG2GEND-B041(容量32GB、eMMC 4.4規范、MMC 5.0兼容、工作電壓1.8V/3.3V)作為主存儲,滿足Linux系統與多媒體文件的高吞吐量讀寫需求。eMMC封裝為BGA 153-ball,便于高速PCB走線設計且具有良好熱性能。eMMC的功能在于提供大容量、塊級存儲接口,可直接掛載為文件系統,具有掉電保護、磨損均衡、壞塊管理等特性,適合存儲Linux根文件系統、視頻文件和日志數據等。

三、電源管理電路

全志A10處理器需要多路電壓輸入,包括Core核電壓(DVDD)、IO電壓(AVDD、DVDDIO)等,一般需要以下幾路:1.8V、1.2V、2.5V、3.3V等。為了簡化電源管理設計,常采用TI(德州儀器)TPS65910B 或 Maxim(美信)MAX77686等PMIC(電源管理集成芯片)來集中生成各路所需電壓。在本文參考設計中,選用TI TPS65910B(支持3A DC/DC降壓、1.5A LDO、I2C可編程、封裝:QFN40)。之所以選擇TPS65910B,一方面是因為該器件具有高集成度、能通過I2C總線動態調整輸出電壓,有助于系統供電優化;另一方面,TI的電源方案在社區中應用廣泛,對其電路拓撲、布局要點都有成熟的參考設計;此外,該芯片內部具備過流、過溫、短路保護功能,能提升供電安全性。TPS65910B可生成1.2V(CPU核心)、1.8V(DDR2控制器)、2.5V(PHY)、3.3V(外設IO)等輸出。為了配合PMIC,還需在輸入端設計一個穩定的5V/3A外部適配器輸入接口,使用肖特基二極管作反接保護,型號選用SS14(1A、40V、SMA封裝),理由是其正向壓降低、工作頻率高、熱性能佳,能夠在電源接反時保護后續電路;同時在板載提供一個Micro USB或DC插座,用于連接外部5V適配器。

在PMIC輸出之后,還需在關鍵節點如DDR2電源、CPU核心電壓等位置添加陶瓷電容(如Murata陶瓷電容,規格:0603封裝、10μF/6.3V 或 22μF/10V),用于去耦與濾波,保證瞬態響應速度;此外,芯片外圍應增加電感與電容網絡以構建Buck降壓拓撲,從而穩定輸出。以生成1.2V為例,TPS65910B內部集成Buck控制器,外部需要配合一顆4.7μH、最大電流4A的電感(如TDK SPM6530-4R7M)與高品質肖特基二極管(如SS14),還能進一步提高電源效率與降低發熱。上述電感選型理由在于額定電流需大于CPU峰值電流(約2A左右),封裝尺寸與易獲取性兼顧;同時電感直流電阻(DCR)越低功耗越小。

四、時鐘電路設計

時鐘電路對于處理器及外設的穩定運行至關重要。全志A10內部需要提供24MHz的主晶振,用于CPU PLL與高速總線時鐘。此外,為滿足DDR2 SDRAM的時序要求,還需提供一個可根據時鐘樹倍頻生成的200MHz用于DRAM控制器。具體設計中,我們在PCB上布置一顆24.000MHz ±30ppm的晶體振蕩器(型號:Abracon ABLS-24.000MHZ-B4-T),使用兩顆貼片電容(22pF/0603封裝)、0Ω電阻做旁路調試,保留電路可修改貼片電容值或更換晶振標稱值以應對后期設計變動。如若應用場景對DDR時序要求較高,可考慮將200MHz參考時鐘通過XO(晶體振蕩器)與PLL產生,而A10內部PLL會將24MHz倍頻為1.2GHz CPU主頻以及DDR2控制時鐘。選用ABLS-24.000MHZ-B4-T的理由在于其集成金屬封裝、抗干擾能力強、溫漂小,且售價合理、易購買。為了保證時鐘信號質量,晶振與處理器之間走線長度控制在3mm以內,并采用差分式GND回流設計,以降低抖動;同時引腳附近采用地平面完整性設計,避免VCC與GND分層導致。對于USB PHY、以太網PHY等外設,也需在PCB上放置相應的25MHz或50MHz晶振,常見型號為Fox Electronics XO XOCH 25.000MHz(I2S解碼器等外設同理),理由是該產品抖動低且封裝易于手工焊接,滿足USB 2.0高速PHY的時鐘需求。

五、以太網及網絡接口

全志A10集成GMAC網絡控制器,可通過外置PHY芯片與RJ45插座相連,實現千兆或百兆以太網功能。在參照設計中,選用Marvell(美滿)88E1116R PHY(支持10/100Mbps,封裝:QFN24),理由是該芯片性能穩定、支持自動協商與MDI/MDIX切換、功耗低,同時其廠商提供完整的參考PCB布局與IN/OUT濾波網絡。PHY芯片與RJ45之間需使用集成磁性模塊,一般型號為Würth Elektronik 749011024(10/100Mbps,以太網Eddy ETF MAGNETICS),該模塊集成磁性元件、隔離變壓器與ESD保護,可簡化電路設計并提高抗干擾性能。所選磁性模塊支持2kV共模抑制,滿足IEC 61000-4-5浪涌標準。PHY與SoC之間通過MII或RMII總線連接,此處建議使用RMII接口,以減少PCB引腳數量與走線復雜度。RMII時鐘(50MHz)需從PHY輸出,并在SoC相應引腳輸入,PCB布局時要保證時鐘與數據線走線長度差異不超過100ps,以免出現時序錯誤。

為了進一步完善網絡功能,設計中可在以太網端口處添加一個外置POE接收模塊(如Microchip PD69224),如果應用場景需要通過以太網線供電則可選用此方案。PD69224集成了PD控制器與DC-DC升壓模塊,可將以太網線48V通過DC-DC轉換為5V供給開發板。但此項為可選功能,根據產品定位決定是否加入。若只需普通網絡通信,可省略POE模塊,從而節省BOM成本。PHY芯片周圍還需配置一些濾波電容、電感以及在PHY VDDIO端添加0.1μF陶瓷電容與4.7μF陶瓷電容做去耦,以穩定信號質量。RJ45插座選用帶LED指示燈的全向防水款(型號:Keystone 5001-2),利于用戶直觀了解鏈路狀態。

六、USB接口設計

全志A10提供兩個USB Host接口與一個USB OTG接口,可同時滿足外接U盤、Wi-Fi模塊、攝像頭等需求。在硬件設計中,推薦使用USB Type-A母座(型號:USB-31-AB-683-TK,Amphenol聯塑),并在VBUS線上加入熔斷式保險絲(型號:PolySwitch RXE050/24,下限阻值約為0.5Ω,電流50mA),以防止外接設備過流損壞主板。為了保護USB信號線免受ESD沖擊,需在D+、D?數據線上分別接上一顆ESD保護二極管(型號:ON Semiconductor ESD5B5V5,封裝SOD-523),其額定電壓5.5V、容量100pF,能有效吸收靜電放電,使信號質量不受影響。USB Host與USB OTG的差異在于OTG具備設備與主機雙重角色,可通過ID引腳識別插頭類型。為實現OTG功能,需在USB OTG口的ID引腳配置10kΩ下拉電阻(型號:Yageo RC0603FR-0710KL),使得插入OTG線纜時設備狀態自動切換。

USB接口信號線走線需采用差分線對結構,線寬線距設計為90μm/90μm,以實現45Ω差分阻抗。信號線長度應保持一致,差異不超過5mm,此外應避免跨越大面積地分割或電源層,以降低信號串擾。VBUS線與GND線在PCB上應盡量粗壯,以承載最大500mA輸出電流。USB接口旁需提供一個微型電源指示LED(型號:Kingbright WP710A10GD,3mm黃綠色,工作電壓2V、20mA)以提示VBUS是否正常輸出。

七、顯示接口設計

A10處理器內置HDMI 1.3輸出,可驅動1080p顯示器。為了實現HDMI輸出,需要在開發板上提供一個標準Type-A HDMI母座(型號:Amphenol 13033911),并在TMDS信號線上分別配置24Ω的差分終端匹配電阻(型號:Würth 150060R247FTL),以及相應的四組100Ω差分去耦電阻(分別分布于信號源與HDMI插座之間,以抑制反射與保證信號完整性)。TMDS對是四對高速差分對,包括CLK+/-、D0+/-、D1+/-、D2+/?。在HDMI插座的電源對地處需增加一個10μF/6.3V的陶瓷去耦電容,用于為HDMI接口芯片內置的5V供電提供穩定電流。若需支持CEC(Consumer Electronics Control)功能,可在CEC線(Pin13)與SoC相應GPIO之間加入一個系列5.1kΩ電阻,以保護GPIO免受直接大電流沖擊。若需支持HDCP及音頻輸出,需在軟件層面配置A10 SoC內置AVI InfoFrame與音頻信息幀。此處的硬件部分主要依賴于SoC內置的PHY,故無需外部時鐘。HDMI插座背面還需預留一個5V輸出,用于給外接HDMI設備供電,上面需串聯一個0.5Ω的熔斷保險絲(PolySwitch RXE050/24)。HDMI信號走線需盡量短,且避免與其他高頻信號平行布置,差分阻抗需嚴格控制在100Ω±10%。

對于LCD平板顯示屏接口,可利用A10的RGB或者LVDS接口。如果選用24位RGB并行接口,則需在主板上提供一個40針FPC連接器(型號:Hirose FH12-40S-0.5SH)并在信號線上進行走線匹配,避免數十根線之間的時序錯位。若需要低功耗、大分辨率的工業級顯示屏,可選用TI SN65LVDS83B LVDS串并轉換芯片,將RGB并行信號轉換為LVDS差分信號,并驅動LVDS接口屏。在該設計中,如果選用LVDS方案,需要在PCB上放置SN65LVDS83B(封裝:QFN24),以及若干匹配電阻與外部電源濾波電容(10μF/10V、0.1μF/50V),同時注意LVDS信號對之間間距要遵循差分對規范。該方案雖然增加了成本與PCB布局難度,但可支持更長距離傳輸與更好的抗干擾性。

八、存儲接口設計

除了上述DDR2 SDRAM及eMMC存儲,還需在開發板上預留常見的外部存儲接口,以滿足擴展需求。常見的設計包括SD/MMC卡插槽、 SATA接口(若A10主控板載支持SATA),以及SPI FLASH。本文參考設計中,保留一個microSD卡插槽(型號:Hirose DF12-8DP-2V)并將其信號線與SoC的SDIO接口相連,以支持系統引導或用戶擴展存儲。由于SDIO接口速度可達50MHz,須在PCB上保證SDCLK、CMD、DAT[3:0]等五根線的差分阻抗與時序匹配,同時CMD與DAT線之間要避免過多交叉。插槽上需配置上拉電阻(10kΩ,型號:Yageo RC0603FR-0710KL)在CMD線與DAT線上,以保持空閑狀態下信號不會漂浮。

若需要支持SATA接口,可通過A10的ATA Host接口配合橋接芯片(如JMicron JMS567 USB3.0轉SATA橋)實現,但若設計重點為成本與簡化PCB布局,可直接省略SATA。在某些定制化應用場景下,為了滿足實時日志記錄或視頻存儲需求,可在板載增加一顆128Mb的SPI NOR Flash(如Macronix MX25L12835F,封裝:WSON8),作為啟動Loader或存儲少量系統配置與日志使用,其優點在于體積小、成本低、可通過SPI總線快速升級固件。與A10的SPI0接口相連時,需在CS、CLK、MOSI、MISO各線加上47Ω系列電阻(型號:Yageo RC0603FR-0747RL),以減小信號振鈴,同時在芯片電源端并聯10μF/4V及0.1μF/6.3V的去耦電容,保證SPI總線在高頻操作下的穩定性。

九、音頻接口設計

全志A10具備I2S總線,可與外部音頻CODEC芯片連接,實現音頻輸入與輸出功能。參考設計中,選用TI TLV320AIC3104(封裝:QFN32),這是一款低功耗、集成麥克風前置放大與耳機驅動器的音頻CODEC,支持立體聲采樣率至48kHz。選擇TLV320AIC3104的原因在于其提供兩個ADC通道與兩個DAC通道,能夠連接麥克風、耳機與外部音響,同時內部集成多種濾波器與數字音量控制,通過I2C或SPI總線配置寄存器。此外,其支持主/從模式,可靈活匹配A10的I2S接口時鐘。該芯片電源需提供3.3V與1.8V,3.3V供給模擬前端,1.8V供給數字核心;在PCB布局時,要將模擬地與數字地分離,并在接地處通過單點連接方式歸并,以降低噪聲耦合。旁路電容建議在每個電源引腳處放置0.1μF/16V(陶瓷)與4.7μF/6.3V(陶瓷)并聯,以兼顧高頻與低頻去耦需求。

為了實現耳機插孔功能,可在開發板上布置一個3.5mm音頻插座(型號:CUI SJ1-3515NG),并在插孔檢測引腳處配置一個22kΩ下拉電阻(型號:Yageo RC0603FR-0722KL),當插入插頭時,SoC可通過該信號檢測到耳機插入狀態,以動態切換音頻輸出。音頻輸出線(L/R)需串聯100Ω或150Ω匹配電阻(型號:Yageo RC0603FR-07150RL),用于限流與阻抗匹配;同時加上一個0.1μF耦合電容(陶瓷)用于直流隔離。麥克風輸入部分可在麥克風偏置線上加上2.2kΩ電阻(型號:Yageo RC0603FR-072K2L),向外部插入麥克風供電,并在輸入通路中加置10μF電解電容(如Nichicon UHE1E100MCL)用于直流隔離,確保音頻信號中無DC偏置進入ADC。

十、調試與擴展接口

為了便于軟件開發與系統調試,開發板上需預留若干調試接口,包括串口UART、JTAG/SWD調試接口以及通用GPIO擴展排針。UART接口通常使用TTL電平(3.3V),連接到A10的UART0(TxD0/RxD0)。在板上布置一個2×5排針插座(Pitch:2.54mm,型號:Samtec TSW-205-07-T-D),并將其中的TX、RX、GND、VCC(3.3V)映射出來,方便用戶通過USB轉TTL線纜與PC通信。為了保護UART電路,在Tx/Rx線上各并聯一個47Ω系列電阻(型號:Yageo RC0603FR-0747RL),以抑制信號沖擊與限流。JTAG/SWD接口選用標準20針ARM Cortex調試排針(型號:Header, Samtec PE-110-02-T-D),其中SWDIO/SWCLK與NRST等引腳連接到A10的調試引腳,方便現場調試與下載固件。若用戶不使用JTAG,可在PCB布局時提供一個0Ω跳線,備用于斷開JTAG電路以將板載資源復用為其他GPIO。

為滿足各種外設擴展需求,可在開發板上預留一個2.54mm排針(一般為2×20或2×26),映射A10的所有GPIO引腳(包括I2C、SPI、PWM、ADC等)。排針上每個GPIO信號都需并聯一個10kΩ上拉電阻(型號:Yageo RC0603FR-0710KL),以保證空閑時信號穩定;此外,在每個I2C引腳(SCL/SDA)上應并聯4.7kΩ上拉電阻(型號:Yageo RC0603FR-074K7L),符合I2C總線要求。為了保護擴展接口不受誤操作損壞,可以在每個GPIO線上加入一個系列電阻(如100Ω,型號:Yageo RC0603FR-07100RL),可減少過流風險。若要支持更多CORD-RUN等擴展,也可在排針附近預留若干位置用于電平轉換芯片(如TXS0108EPWR),以實現5V或1.8V外設的兼容。

十一、PCB布局與走線注意事項

開發板PCB采用四層或六層堆棧結構,其中頂層為信號層,底層為信號層,中間兩層分別為地層與電源層(如1.8V、3.3V)。在布局時,應遵循以下要點:首先,將大尺寸元器件如A10 SoC、DDR2 SDRAM、eMMC FLASH集中放置在板中央,保證PCB分區合理;其次,電源管理PMIC放置在SoC涌現熱量較大的區域附近,以縮短電源走線長度;再次,將晶振與SoC的時鐘輸入接口盡量靠近擺放,以減少時鐘線長度。各高速差分對(如DDR2、USB、HDMI、LVDS等)需在同一層走線,并保持差分阻抗匹配,布線時切忌跨層跳線過多;而在跨層時必須使用盲孔或埋孔,并保證過孔數量對稱分布,以降低串擾與信號延遲。地層需盡可能完整,避免切割大面積地平面,以形成良好的回路;對于需要與模擬電路分隔的區域(如音頻CODEC、ADC等),可在地層中采用隔離,但在單點處與數字地相連接,以實現統一參考地。

為了提高板上散熱性能,A10 SoC正下方應貼合一片專用散熱銅箔或固化絕緣散熱片,通過散熱孔與底層大面積散熱網拼接;同時在PCB上設計散熱擋片,將板載溫度控制在85°C以下。電源管理芯片的周圍也需留出足夠的銅箔面積,用于熱擴散。PCB上每個去耦電容應盡量靠近相應供電引腳,并且與地平面形成最短回路;地與電源層之間應預留充足的鏤空過孔(VIAs),以實現多層過孔的散熱與去耦。

一般開發板尺寸建議為100mm×100mm或更為經濟的80mm×80mm,可根據應用場景決定實際尺寸。若需支持DIN導軌式安裝,可將PCB設計為長條形,并按照工業標準預留螺絲定位孔。

十二、結論與參考資料

本文以全志A10開發板為核心,詳細介紹了基于全志A10 SoC的開發板設計方案與原理圖要點,包含核心處理器與存儲部分、電源管理、時鐘電路、網絡與USB接口、顯示接口、存儲擴展、音頻功能、調試接口以及PCB布局注意事項等方面的內容。文中列舉的元器件型號如全志A10芯片、Micron DDR2 SDRAM、TI TPS65910B PMIC、Winbond NOR Flash、Samsung eMMC、Marvell PHY、TI音頻CODEC 等均為市場主流且具備良好社區支持的產品,選型理由基于性能穩定、成本合理、文檔支持豐富以及封裝易于布線等多項考慮。希望本文檔能為開發者在進行A10相關項目設計時提供切實可行的參考,減少方案驗證周期,加速產品開發進程。

若需獲取具體的原理圖與PCB源文件,可訪問全志A10官方文檔或各大開源社區。例如,在Allwinner官網與Baidu HiTalk論壇、GitHub等平臺均可查找開源的A10開發板設計資料,下載時請關注版本與許可證信息,并根據自身項目需求進行二次開發與修改。

責任編輯:David

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)