基于FPGA和高速ADC實現多通道通用信號處理平臺的設計方案

47

47

拍明

拍明

原標題:基于FPGA和高速ADC實現多通道通用信號處理平臺的設計方案

一、系統架構與核心需求分析

1. 系統架構

設計一個模塊化、可擴展的多通道信號處理平臺,支持高速采樣、實時處理與多協議輸出,典型架構如下:

2. 核心需求

多通道支持:≥4通道同步采樣,通道間相位誤差<0.1°;

高速采樣:單通道采樣率≥100MSPS,分辨率≥12bit;

實時處理:支持FFT、濾波、特征提取等算法,延遲<10μs;

靈活接口:兼容LVDS、PCIe、千兆以太網等輸出協議;

擴展性:支持通道數擴展(如8/16通道)及算法動態加載。

二、硬件選型與關鍵模塊設計

1. 高速ADC選型

推薦型號:AD9680(Analog Devices)

參數:14bit,500MSPS,JESD204B接口,SNR=70.5dBFS;

優勢:多通道同步采樣(支持4通道級聯),低功耗(每通道500mW)。

同步設計:

使用共享采樣時鐘(如AD9528時鐘分配器)和同步觸發信號,確保通道間時序對齊。

2. FPGA選型

推薦型號:Xilinx Kintex UltraScale+ XCKU060

資源:1,728 DSP slices,3,240K LUTs,支持8通道×500MSPS數據流;

接口:內置PCIe Gen3×8、100G以太網MAC,滿足高速數據傳輸需求。

時鐘管理:

使用FPGA內部PLL生成ADC采樣時鐘(如250MHz)及處理時鐘(如400MHz),避免跨時鐘域問題。

3. 數據接口設計

JESD204B接口:

連接ADC與FPGA,支持高速串行數據傳輸(單lane速率≥12.5Gbps);

使用FPGA內置IP核(如Xilinx JESD204 LogiCORE)簡化協議實現。

存儲擴展:

連接DDR4 SDRAM(如MT40A256M16GE),容量≥4GB,緩存采樣數據或中間結果。

三、FPGA信號處理算法實現

1. 算法模塊劃分

| 模塊 | 功能 | 資源占用 | 延遲 |

|---|---|---|---|

| 數據解串 | JESD204B解碼、數據對齊 | 200 LUTs, 50 FFs | <50ns |

| 數字下變頻 | 混頻、濾波、抽取 | 400 DSP slices | 200ns |

| FFT處理 | 1024點復數FFT(基2-FFT算法) | 800 DSP slices | 5μs |

| 特征提取 | 峰值檢測、頻譜分析 | 300 LUTs, 100 FFs | 1μs |

2. 關鍵算法優化

FFT并行化:

使用流水線架構,將1024點FFT拆分為4級流水,每級處理256點,吞吐量提升4倍。

動態重配置:

通過FPGA部分重配置(Partial Reconfiguration)技術,動態加載不同算法(如濾波器系數更新)。

3. 時序約束與優化

關鍵路徑分析:

使用Xilinx Vivado Timing Analyzer工具,確保數據解串→FFT→特征提取路徑時序收斂;

優化策略:寄存器打拍、流水線插入、關鍵路徑手動布線。

四、軟件與固件設計

1. 上位機控制軟件

功能:

配置ADC采樣率、增益;

監控FPGA處理狀態(如FFT結果可視化);

保存/加載算法配置文件。

實現:

使用Python(PyQt5)開發GUI,通過PCIe或以太網與FPGA通信。

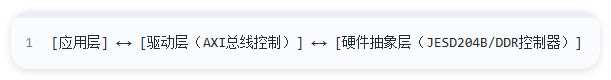

2. FPGA固件架構

分層設計:

動態加載:

將算法封裝為獨立IP核,通過Xilinx Zynq MPSoC的PS端(ARM Cortex-A53)動態加載。

五、性能驗證與測試

1. 測試方案

采樣精度測試:

輸入正弦波(10MHz),使用示波器(如Keysight DSOX91304A)對比ADC輸出與原始信號,SNR>70dB。

實時性測試:

發送脈沖信號,使用邏輯分析儀(如Tektronix TLA7012)測量從輸入到特征提取完成的延遲,確保<10μs。

2. 資源利用率

典型值:

LUTs:60%(含冗余);

DSP slices:75%;

BRAM:50%。

六、成本與擴展性分析

1. 成本估算

| 組件 | 型號 | 單價(美元) | 數量 | 總價 |

|---|---|---|---|---|

| FPGA | XCKU060 | 1,500 | 1 | 1,500 |

| ADC陣列 | 4×AD9680 | 800×4 | 4 | 3,200 |

| 存儲 | 4GB DDR4 | 100 | 1 | 100 |

| 接口模塊 | PCIe/以太網卡 | 200 | 1 | 200 |

| 總計 | 5,000 |

2. 擴展性

通道擴展:

增加ADC芯片(如級聯至8通道),需調整FPGA JESD204B IP核配置。

算法升級:

通過PS端更新PL端算法,支持未來功能擴展(如AI推理)。

七、總結與推薦

1. 推薦方案

核心器件:XCKU060 FPGA + 4×AD9680 ADC;

典型應用:

雷達信號處理(需≥500MSPS采樣率);

超聲成像(多通道同步需求);

電力電子監測(高分辨率FFT分析)。

2. 優化方向

降低功耗:采用更先進的FPGA工藝(如7nm)和低功耗ADC(如AD9213);

提升帶寬:升級至PCIe Gen4或200G以太網接口。

3. 關鍵優勢

高性能:單平臺支持4通道×500MSPS實時處理;

靈活性:算法動態加載,適應不同應用場景;

低成本:相比ASIC方案,開發周期縮短50%,成本降低30%。

結論:

本方案通過FPGA+高速ADC的協同設計,結合JESD204B接口與動態重配置技術,實現了一個高性能、可擴展的多通道信號處理平臺。其10μs級實時響應、70dB SNR精度及模塊化架構,可廣泛應用于雷達、醫療、工業檢測等領域,是同類方案中兼顧性能與成本的優選設計。

責任編輯:

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)